# Integration tests with Global Muon Trigger

# Tobias Nöbauer and Ivan Mikulec HEPHY Vienna

CMS Trigger meeting 31 January 2006

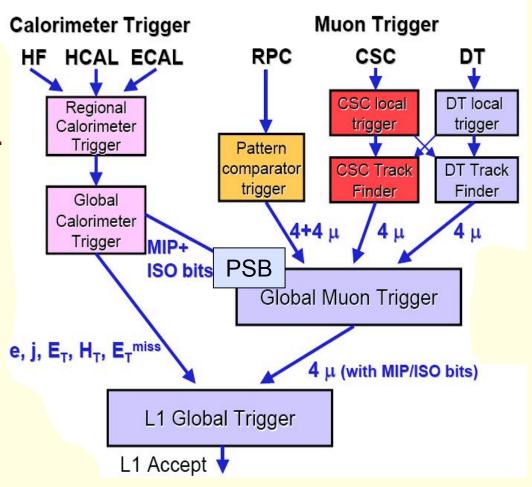

### Overview

- GMT Self-tests

- GMT Integration tests

- Test with PSB

- Test with DTTF

- Test with CSCTF

- SW activities

- Conclusions

### **GMT Self-tests**

- Self-tests of the GMT module were done in Vienna using ORCA data (H→ZZ→4µ)- full internal functionality reproduced (apart from 4 bit errors - 2 corrected in the firmware)

- Mid-December GMT module arrived at CERN

- Before Christmas self-tests were repeated in b. 904

- From the beginning of January GMT was ready for integration

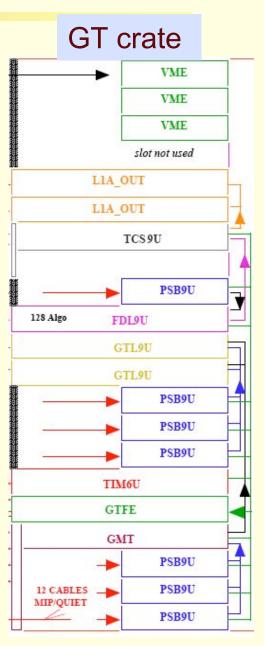

### Test with PSB

- PSB (Pipelined Synchronising Buffer) synchronises the GCT inputs into GT and GMT

- Only one PSB board available at CERN for the moment (3 PSBs foreseen for the GMT input)

- Test was done using special ORCA data:

- modified to account for one PSB only

- MIP/ISO information written into the PSB board

- Muon inputs written into GMT simulation memories in the input FPGA's

- Timing (clock and BCreset) provided by the GT TIM module

- After a fine timing adjustment, data were received and combined by the GMT correctly

- A couple of transmission bit errors found

- Tobias is preparing new test firmware to localise these bit errors

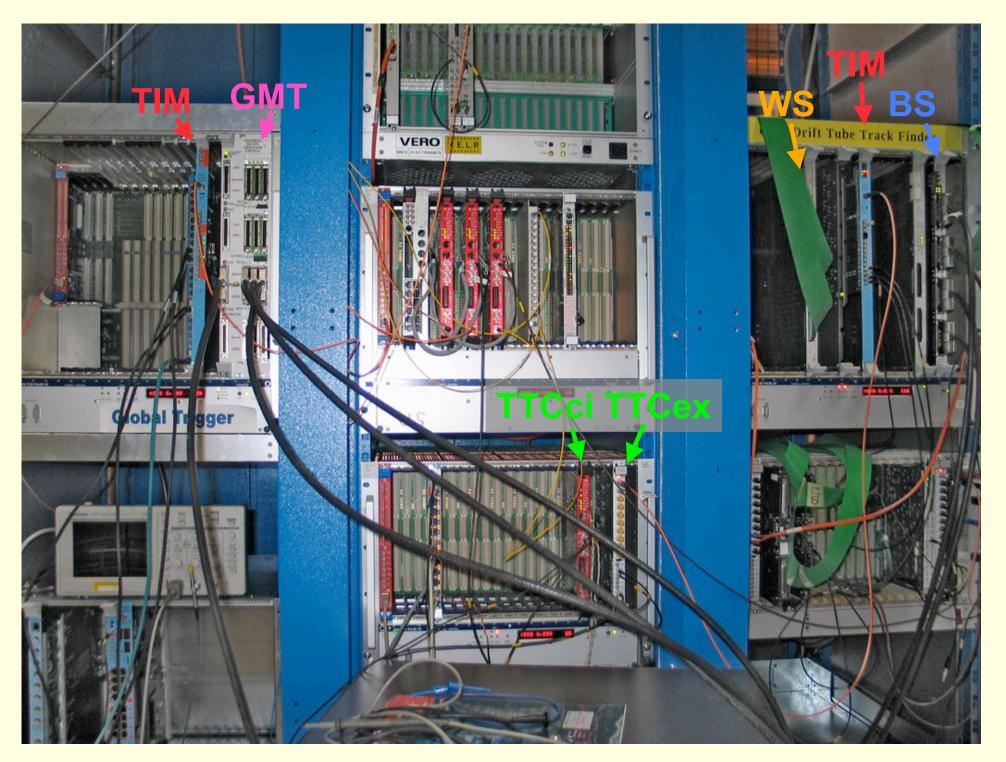

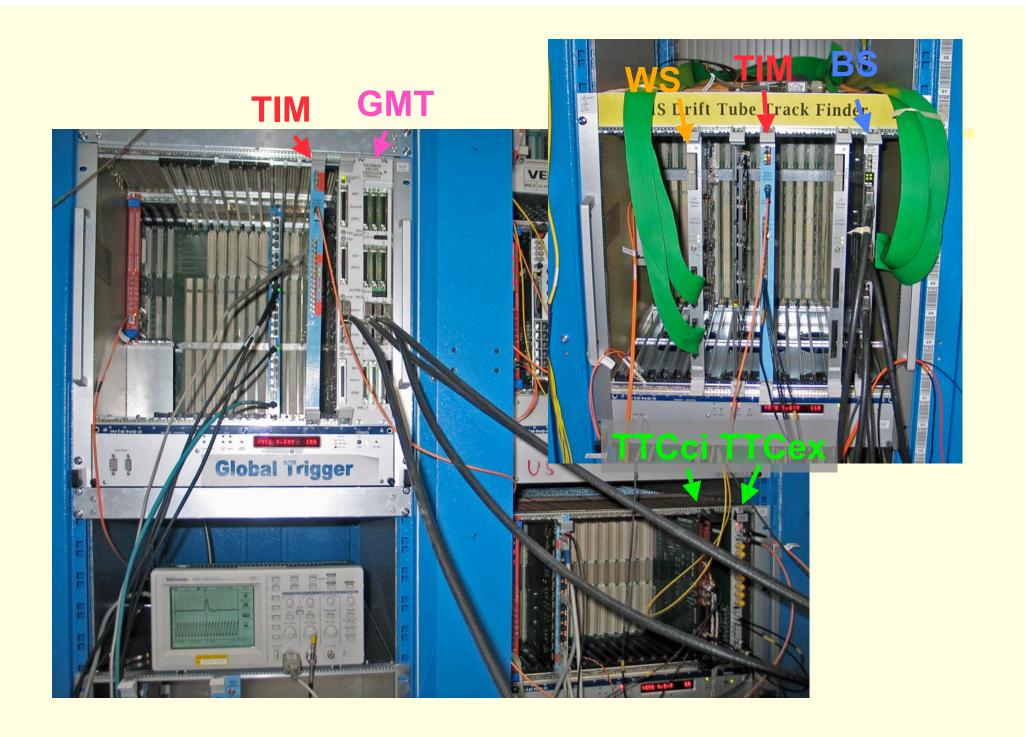

### Test with DTTF

- In collaboration with Janos

- Bit patterns sent from Wedge Sorter (WS) through Barrel Sorter (BS) into GMT

- Common clock provided by TTCci and split by TTCex (thanks to Jan for his assistance) and received by TIM modules in both crates

- All 16 GMT input connectors were scanned (4 bit errors in total found on the GMT side)

- Next step is to try to connect more modules in a chain and use ORCA data

I. Mikulec: GMT Integration

### Test with CSCTF

- Mid-January the new CSC Muon Sorter board (MS2005) arrived at CERN

- Dan installed it in the CSCTF crate

- It was self-tested remotely by Sang-Joon Lee from Rice

- Our interconnection test was synchronised using TTCci/TTCex system connected to TIM board in the GT crate and CCB (Clock and Control Board) in the CSCTF crate:

- Test pattern was written into MS RAMs

- The transmission was triggered by a BC0 broadcast from TTCci

- The same signal triggered reading of spy memories in the GMT input FPGA

- Data were aligned for comparison with appropriate delay

- No problems have been found

I. Mikulec: GMT Integration

### SW activities

- On the fly development of test SW for the integration activities in b. 904

- New firmware with updated LUTs

- Test firmware for MIP/ISO FPGas

- Integration to Trigger Supervisor

- Configuration database

## Layout of the GMT config. db

### GMT\_FIRMWARE

FW\_KEY\_VARCHAR2(32) NOT NULL (PK) VERSION NUMBER(32) NULL URL VME VARCHAR2(512) NULL URL\_JAL\_VARCHAR2(512) NULL URL\_BYTEBLASTER VARCHAR2(512) NULL DESCRIPTION VARCHAR2(512) NULL

### GMT\_INX\_REGISTERS

IF\_REG\_KEY\_VARCHAR2(32) NOT NULL (PK) IF\_SYNCCONFIGREG\_ADDRO NUMBER(5) NULL IF\_SYNCCONFIGREG\_ADDR1\_NUMBER(5) NULL IF\_SYNCCONFIGREG\_ADDR2 NUMBER(5) NULL IF\_SYNCCONFIGREG\_ADDR3\_NUMBER(5) NULL IF\_READOUTSYNCREG\_ADDR\_NUMBER(5) NULL IF\_LATDELAYREG\_ADDR\_NUMBER(5) NULL IF\_SIMUSPYCONFIG\_ADDR\_NUMBER(5) NULL IF\_SPYDEPTH\_ADDR\_NUMBER(5) NULL IF\_SPYARMPULSE\_WADDR\_NUMBER(5) NULL IF\_COMPARECOUNTERRESET\_WADDR\_NUMBER(5) NULL DESCRIPTION VARCHAR2(512) NULL

### GMT\_LFX\_REGISTERS

LF\_REG\_KEY VARCHAR2(32) NOT NULL (PK) LF\_CDLCONFIG\_ADDRO\_NUMBER(5) NULL LF CDLCONFIG ADDR1 NUMBER(5) NULL LF\_SORTRANKOFFSET\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_SRK\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_PHI\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_ETA\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_PT\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_CHARGE\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_MIP\_ADDR\_NUMBER(5) NULL LF\_MMCONFIG\_ISO\_ADDR\_NUMBER(5) NULL DESCRIPTION VARCHAR2(512) NULL

### GMT\_SRT\_REGISTERS

SF\_REG\_KEY\_VARCHAR2(32) NOT NULL (PK) SF\_READOUTSYNCREG\_ADDR\_NUMBER(5) NULL SF\_LATDELAYREG\_ADDR\_NUMBER(5) NULL SF\_SIMUSPYCONFIG\_ADDR\_NUMBER(5) NULL SF\_SPYDEPTH\_ADDR\_NUMBER(5) NULL SF\_SPYARMPULSE\_WADDR\_NUMBER(5) NULL DESCRIPTION VARCHAR2(512) NULL

### GMT\_CONFIG

GMT\_KEY\_VARCHAR2(32) NOT NULL (PK) INB\_FW\_KEY VARCHAR2(32) NOT NULL (FK) INB\_REG\_KEY VARCHAR2(32) NOT NULL (FK) INC\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) INC\_REG\_KEY VARCHAR2(32) NOT NULL (FK) IND\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) IND\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) INF\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) INF\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) AUF\_FW\_KEY VARCHAR2(32) NOT NULL (FK) AUF\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) AUF\_LUTS\_KEY VARCHAR2(32) NOT NULL (FK) AUB\_FW\_KEY VARCHAR2(32) NOT NULL (FK) AUB\_REG\_KEY VARCHAR2(32) NOT NULL (FK) AUB LUTS KEY VARCHAR2(32) NOT NULL (FK) LFF\_FW\_KEY VARCHAR2(32) NOT NULL (FK) LFF\_REG\_KEY VARCHAR2(32) NOT NULL (FK) LFF\_LUTS\_KEY\_VARCHAR2(32) NOT NULL (FK) LFB\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) LFB\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) LFB\_LUTS\_KEY VARCHAR2(32) NOT NULL (FK) SRT\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) SRT\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) ROP\_FW\_KEY\_VARCHAR2(32) NOT NULL (FK) ROP\_REG\_KEY\_VARCHAR2(32) NOT NULL (FK) DESCRIPTION VARCHAR2(512) NULL

### GMT\_ROP\_REGISTERS

ROP\_REG\_KEY\_VARCHAR2(32) NOT NULL (PK) ROP\_RESET\_ADDR\_NUMBER(5) NULL ROP\_RESET\_DCM\_ADDR\_NUMBER(5) NULL ROP\_COMMAND\_ADDR\_NUMBER(5) NULL ROP\_TAG\_ENABLE\_ADDR\_NUMBER(5) NULL ROP\_PROG\_ENABLE\_ADDR\_NUMBER(5) NULL ROP\_NPROG\_ADDR\_NUMBER(5) NULL ROP\_INIT\_CMD\_ADDR\_NUMBER(5) NULL ROP\_DIN\_INF\_ADDR\_NUMBER(5) NULL ROP\_DIN\_INC\_ADDR\_NUMBER(5) NULL ROP\_DIN\_IND\_ADDR\_NUMBER(5) NULL ROP\_DIN\_INB\_ADDR\_NUMBER(5) NULL ROP\_DIN\_AUF\_ADDR\_NUMBER(5) NULL ROP\_DIN\_LFF\_ADDR\_NUMBER(5) NULL ROP\_DIN\_LFB\_ADDR\_NUMBER(5) NULL ROP\_DIN\_AUB\_ADDR\_NUMBER(5) NULL ROP\_DIN\_SRT\_ADDR\_NUMBER(5) NULL ROP\_DUMMY\_CMD\_ADDR\_NUMBER(5) NULL ROP\_LATDELAYREG\_ADDR\_NUMBER(5) NULL ROP\_VMEWRITEALLMASK\_ADDR\_NUMBER(5) NU DESCRIPTION VARCHAR2(512) NULL

### GMT\_AUX\_REGISTERS

MIAU\_REG\_KEY\_VARCHAR2(32) NOT NULL (PK) MIAU\_READOUTSYNCREG\_ADDR\_NUMBER(5) NULL MIAU\_SIMUSPYCONFIG\_ADDR\_NUMBER(5) NULL MIAU\_SPYDEPTH\_ADDR\_NUMBER(5) NULL MIAU\_SPYARMPULSE\_WADDR\_NUMBER(5) NULL DESCRIPTION VARCHAR2(512) NULL

### GMT\_LFX\_LUTS

LF\_LUTS\_KEY\_VARCHAR2(32) NOT NULL (PK) LF\_MATCHQUALLUT\_BASE0 VARCHAR2(512) NULL LF\_MATCHQUALLUT\_BASE1 VARCHAR2(512) NULL LF\_MATCHQUALLUT\_BASE2 VARCHAR2(512) NULL LF\_COUDELTAETALUT\_BASE0 VARCHAR2(512) NULL LF\_COUDELTAETALUT\_BASE1 VARCHAR2(512) NULL LF\_OVLETACONVLUT\_BASEO\_VARCHAR2(512) NULL LF\_OVLETACONVLUT\_BASE1 VARCHAR2(512) NULL LF\_OVLETACONVLUT\_BASE2\_VARCHAR2(512) NULL LF\_ETACONVLUT\_BASEO VARCHAR2(512) NULL LF\_ETACONVLUT\_BASE1 VARCHAR2(512) NULL LF\_MERGERANKPTQLUT\_BASE0\_VARCHAR2(512) NULL LF\_MERGERANKPTQLUT\_BASE1\_VARCHAR2(512) NULL LF\_PHIPROETACONVLUT\_BASE0\_VARCHAR2(512) NULL LF\_PHIPROETACONVLUT\_BASE1 VARCHAR2(512) NULL LF\_BLOCKRAM\_BASE VARCHAR2(512) NULL LF\_SORTRANKETAQLUT\_BASEO VARCHAR2(512) NULL LF\_SORTRANKETAQLUT\_BASE1 VARCHAR2(512) NULL LF\_SORTRANKPTQLUT\_BASE0 VARCHAR2(512) NULL LF\_SORTRANKPTQLUT\_BASE1 VARCHAR2(512) NULL LF\_SORTRANKETAPHILUT\_BASEO VARCHAR2(512) NULL LF\_SORTRANKETAPHILUT\_BASE1 VARCHAR2(512) NULL LF\_SORTRANKCOMBINELUT\_BASE0 VARCHAR2(512) NULL LF\_SORTRANKCOMBINELUT\_BASE1 VARCHAR2(512) NULL LF\_DELTAETALUT\_BASE0 VARCHAR2(512) NULL LF\_PTMIXLUT\_BASEO VARCHAR2(512) NULL LF\_MERGERANKETAQLUT\_BASEO VARCHAR2(512) NULL LF\_MERGERANKETAQLUT\_BASE1 VARCHAR2(512) NULL LF\_MERGERANKETAPHILUT\_BASEO\_VARCHAR2(512) NULL LF\_MERGERANKETAPHILUT\_BASE1 VARCHAR2(512) NULL LF\_MERGERANKCOMBINELUT\_BASEO VARCHAR2(512) NULI LF\_MERGERANKCOMBINELUT\_BASE1 VARCHAR2(512) NULL LF\_DISABLEHOTLUT\_BASE0\_VARCHAR2(512) NULL LF\_PHIPROLUT\_BASEO VARCHAR2(512) NULL LF\_PHIPROLUT\_BASE1 VARCHAR2(512) NULL DESCRIPTION VARCHAR2(512) NULL

### **GMT AUX LUTS**

MIAU\_LUTS\_KEY VARCHAR2(32) NOT NULL (PK) MIAU\_ETACONVLUT\_BASE0 VARCHAR2(512) NUL MIAU\_ETACONVLUT\_BASE1 VARCHAR2(512) NUL MIAU\_ETACONVLUT\_BASE2\_VARCHAR2(512) NUL MIAU\_ETACONVLUT\_BASE3 VARCHAR2(512) NUL MIAU\_PHIPRO1LUT\_BASE0 VARCHAR2(512) NULL MIAU\_PHIPRO1LUT\_BASE1 VARCHAR2(512) NULL MIAU\_PHIPRO1LUT\_BASE2 VARCHAR2(512) NULL MIAU\_PHIPRO1LUT\_BASE3 VARCHAR2(512) NULL MIAU\_PHIPRO2LUT\_BASE0 VARCHAR2(512) NULL MIAU\_PHIPRO2LUT\_BASE1 VARCHAR2(512) NULL MIAU\_PHIPRO2LUT\_BASE2 VARCHAR2(512) NULL MIAU\_PHIPRO2LUT\_BASE3 VARCHAR2(512) NULL MIAU\_ETAPROLUT\_BASE0 VARCHAR2(512) NULL MIAU\_ETAPROLUT\_BASE1 VARCHAR2(512) NULL MIAU\_ETAPROLUT\_BASE2 VARCHAR2(512) NULL MIAU ETAPROLUT BASES VARCHAR2(512) NULL DESCRIPTION VARCHAR2(512) NULL

### Conclusions

- Integration tests of several trigger chains leading to the GMT have been started in parallel in the integration area of b. 904

- TTCci/TTCex system has been installed and tested in the integration area as a basic synchronisation tool for these tests

- The RPC chain can be tested as soon as RPC electronics is ready (end of February?)

- Tests with DTTF and CSCTF will continue by adding new elements to the chain and using ORCA simulation to calculate the expected response